高速接口与EDA实验室

建设情况、主要技术指标

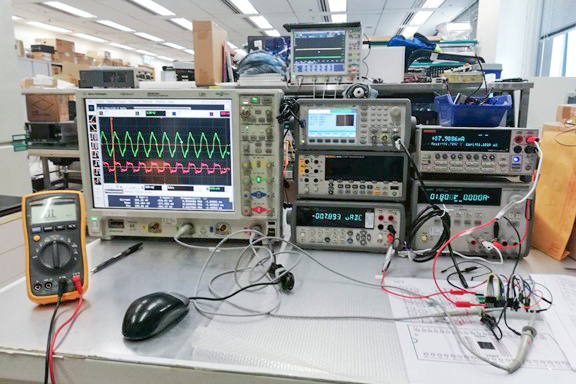

高速接口与EDA实验室拥有Thermo Fisher Scientific公司的TLP(Transmission Line Pulse)测试设备一台,脉冲宽度100ns,上升时间10ns,可以满足一般情况下的ESD器件on-wafer ESD表征。实验室还拥有美国Barth公司的VFTLP一台(Barth 4012),脉冲宽度10ns,上升时间1ns,可以满足CDM脉冲on-wafer表征。除此之外,Lab还配置了系统级ESD测试设备,为系统ESD测试提供了技术保证。

研发开发能力

- 低电容ESD和TVS器件结构

- 通用目的I/O单元库及特殊用途的I/O单元库

- 高速I/O接口电路如MIPI, SerDes, SATA

- 定制化的ESD和TVS器件工艺开发

利用率

95%

实验室利用率超过 95% , 主要用于研究和原型开发工作。

研究(生产)项目和成效

- 与国内领先代工厂合作,帮助开发ESD保护器件

- 遵循40nm ESD设计规则,在不降低ESD能力的前提下,节省ESD面积30%

- 55nm ESD器件开发,HBM能力8kV

- 14/16nm 3D-FinFET GPIO 开发

- 12nm 3D-FinFET RGMII I/O库开发

- 40nm EF平台8kV HMB I/O单元设计

- 高速I/O接口电路研发

面向行业的开放情况

向行业合作伙伴开放,提供测试、咨询服务以及合作研究。