高速接口與EDA實驗室

建設情況、主要技術指標

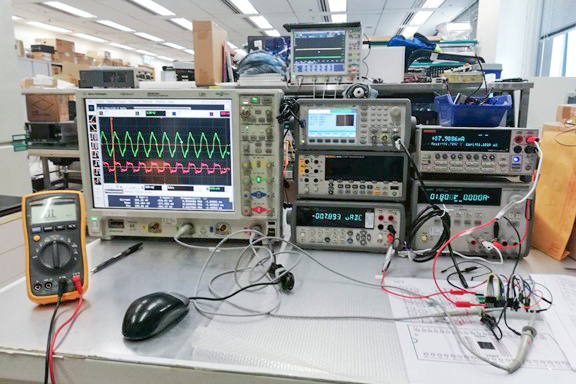

高速接口與EDA實驗室擁有Thermo Fisher Scientific公司的TLP(Transmission Line Pulse)測試設備一台,脈衝寬度100ns,上升時間10ns,可以滿足一般情況下的ESD器件on-wafer ESD表徵。實驗室還擁有美國Barth公司的VFTLP一台(Barth 4012),脈衝寬度10ns,上升時間1ns,可以滿足CDM脈衝on-wafer表徵。除此之外,Lab還配置了系統級ESD測試設備,為系統ESD測試提供了技術保證。

研發開發能力

- 低電容ESD和TVS器件結構

- 通用目的I/O單元庫及特殊用途的I/O單元庫

- 高速I/O接口電路如MIPI, SerDes, SATA

- 定制化的ESD和TVS器件工藝開發

利用率

95%

實驗室利用率超過 95% , 主要用於研究和原型開發工作。

研究(生產)項目和成效

- 與國內領先代工廠合作,幫助開發ESD保護器件

- 遵循40nm ESD設計規則,在不降低ESD能力的前提下,節省ESD面積30%

- 55nm ESD器件開發,HBM能力8kV

- 14/16nm 3D-FinFET GPIO 開發

- 12nm 3D-FinFET RGMII I/O庫開發

- 40nm EF平台8kV HMB I/O單元設計

- 高速I/O接口電路研發

面向行業的開放情況

向行業合作夥伴開放,提供測試、諮詢服務以及合作研究。